Automatinė optinė BGA perdirbimo stotis

Plačiai naudojamas taisant lusto lygio pagrindines plokštes mobiliuosiuose įrenginiuose, nešiojamuose kompiuteriuose, televizoriuose, oro kondicionieriuose ir kt. Jis pasižymi dideliu sėkmingu remonto greičiu ir aukštu automatizavimo laipsniu ir sutaupo daug žmonių pastangų. Esame profesionalūs šios mašinos gamintojai ir turime šias mašinas sandėlyje.

Aprašymas

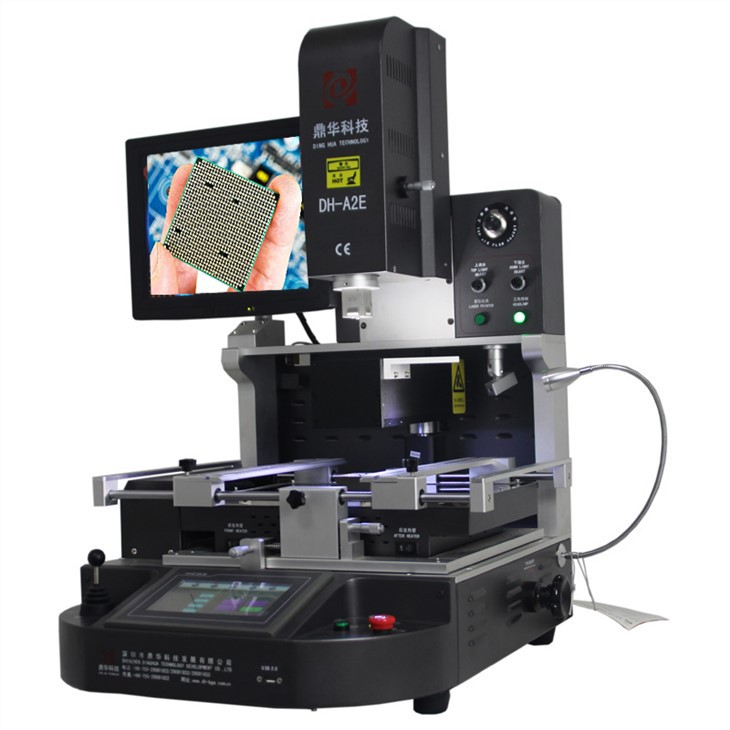

Automatinė optinė BGA perdirbimo stotis

1. Auto Optical BGA Rework Station taikymas

Kompiuterio, išmaniojo telefono, nešiojamojo kompiuterio, „MacBook“ logikos plokštės, skaitmeninės kameros, oro kondicionieriaus, televizoriaus ir kitos elektroninės plokštės pagrindinė plokštė

įranga iš medicinos pramonės, ryšių pramonės, automobilių pramonės ir kt.

Tinka įvairių tipų lustams: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED lustai.

2. Automatinės optinės BGA perdirbimo stoties gaminio savybės

• Didelis sėkmingo lusto lygio taisymo rodiklis. Išlitavimo, montavimo ir litavimo procesas yra automatinis.

• Tikslų kiekvienos litavimo jungties išlygiavimą galima užtikrinti naudojant optinio išlygiavimo CCD kamerą.

•Tikslus temperatūros valdymas gali būti užtikrinamas naudojant 3 nepriklausomas šildymo zonas. Mašina gali nustatyti ir išsaugoti

1 milijonas temperatūros profilio.

• Įmontuotas vakuumas montavimo galvutėje automatiškai paima BGA lustą, kai baigtas litavimas.

3. Auto Optical BGA Rework Station specifikacija

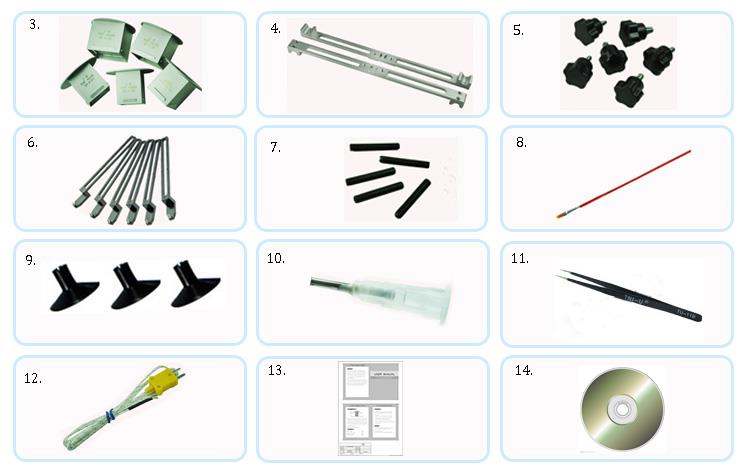

4. Auto Optical BGA Rework Station detalės

CCD kamera (tiksli optinio derinimo sistema); 2.HD skaitmeninis ekranas; 3. Mikrometras (reguliuoti lusto kampą);

4.3 nepriklausomi šildytuvai (karšto oro ir infraraudonųjų spindulių); 5. Lazerinis padėties nustatymas ; 6. HD jutiklinio ekrano sąsaja, PLC valdymas;

7.Led priekinis žibintas ; 8.Vairasvirtės valdymas .

5. Kodėl verta rinktis mūsų automatinę optinę BGA perdirbimo stotį?

6.Auto Optical BGA Rework Station sertifikatas

7. Auto Optical BGA Rework Station pakavimas ir siuntimas

8.DUK

Kaip patikrinti lustą?

Pradinis sistemos lygio lusto bandymas

SoC yra pagrįstas giliais submikroniniais procesais, todėl norint išbandyti naujus Soc įrenginius reikia visiškai naujo požiūrio. Kadangi kiekvienas funkcinis komponentas

turi savo testavimo reikalavimus, projektavimo inžinierius turi sudaryti bandymų planą projektavimo proceso pradžioje.

SoC įrenginių blokų testavimo planas turi būti įgyvendintas: tinkamai sukonfigūruoti ATPG įrankiai loginiam testavimui; trumpas bandymo laikas; naujas greitasis

gedimų modeliai ir kelių atminties arba mažo masyvo testai. Gamybos linijai diagnostikos metodas ne tik nustato gedimą, bet ir atskiria

sugedęs mazgas iš darbinio mazgo. Be to, kai tik įmanoma, norint sutaupyti bandymo laiko, reikėtų naudoti bandomuosius multipleksavimo būdus. Srityje labai

Integruotas IC testavimas, ATPG ir IDDQ testuojami projektavimo metodai turi galingą gedimų atskyrimo mechanizmą.

Kiti faktiniai parametrai, kuriuos reikia planuoti iš anksto, apima kaiščių, kuriuos reikia nuskaityti, skaičių ir atminties kiekį kiekviename kaiščio gale.

Ribų nuskaitymas gali būti įterptas į SoC, bet neapsiriboja plokščių ar kelių lustų modulių sujungimo bandymais.

Nors lusto dydis mažėja, lustas vis dar gali supakuoti nuo milijonų iki 100 milijonų tranzistorių, o bandymo režimų skaičius išaugo iki precedento neturinčio

lygius, todėl bandymų ciklai ilgesni. Šią problemą galima išbandyti. Režimas suspaudimo išspręsti, suspaudimo laipsnis gali siekti 20 procentų iki 60 procentų. Šiandienos didelio masto

lusto dizainas, siekiant išvengti talpos problemų, būtina rasti bandomąją programinę įrangą, kuri gali veikti 64-bit operacinėse sistemose.

Be to, bandomoji programinė įranga susiduria su naujomis testavimo problemomis, kurias sukelia gilūs submikroniniai procesai ir didėjantis dažnis. Anksčiau ATPG bandymo režimas

nebebuvo taikomas statinio blokavimo gedimų tikrinimas. Į tradicinius įrankius įtraukus funkcinius modelius, buvo sunku rasti naujų gedimų. Geresnis požiūris yra

klasifikuokite ankstesnes funkcinių režimų grupes, kad nustatytumėte, kurių gedimų negalima aptikti, tada sukurkite ATPG režimą, kad užfiksuotumėte šiuos trūkstamus gedimų tipus.

Didėjant projektiniam pajėgumui ir mažėjant tranzistoriaus bandymo laikui, siekiant rasti su greičiu susijusias problemas ir patikrinti grandinės laiką, sinchroninis bandymo metodas

turi būti įdarbintas. Sinchroninis bandymas turi apimti kelis gedimų modelius, įskaitant trumpalaikius modelius, kelio delsas ir IDDQ.

Kai kurios pramonės įmonės mano, kad blokavimo, funkcinių ir trumpalaikių / kelio vėlavimo gedimų derinimas gali būti veiksmingiausia bandymo strategija. Dėl gilių

submikronų lustai ir aukšto dažnio veikimas, pereinamojo laikotarpio ir kelio vėlavimo testavimas yra dar svarbesnis.

Norint išspręsti ATE tikslumo problemą sinchronizuojant bandymo branduolį ir sumažinti išlaidas, būtina rasti naują metodą, kuris supaprastintų

bandymo įtaisas (pereinamojo ir kelio vėlavimo testui reikalingas tikslus laikrodis bandymo įrenginio sąsajoje), Jis užtikrina, kad signalas bandymo metu būtų pakankamai tikslus.

Kadangi SoC atminties bloke yra didelė gamybos defektų tikimybė, atminties BIST turi turėti diagnostikos funkciją. Radus problemą,

sugedęs adreso blokas gali būti susietas su atsarginio adreso bloko pertekline atmintimi, o aptikto gedimo adresas bus išmestas. Venkite išmesti

visas brangus lustas.

Išbandžius mažus įterptosios atminties blokus, nebereikia papildomų vartų ar valdymo logikos. Pavyzdžiui, vektoriaus konvertavimo testavimo metodai gali konvertuoti

funkcinius režimus į nuskaitymo režimų seriją.

Skirtingai nuo BIST metodo, apėjimo atminties bloko funkcinis įėjimas nereikalauja papildomos logikos. Kadangi nereikia papildomos testavimo logikos, SoC

kūrimo inžinieriai gali pakartotinai panaudoti anksčiau suformuotus bandymų modelius.

Išplėstiniai ATPG įrankiai ne tik lygiagrečiai tikrina makrokomandas, bet ir nustato, ar nėra konfliktų, taip pat išsamiai nurodo, kurias makrokomandas galima išbandyti lygiagrečiai ir kurias

makrokomandos negali būti išbandytos lygiagrečiai. Be to, šias makrokomandas galima efektyviai išbandyti, net jei makrokomandos laikrodis yra toks pat kaip nuskaitymo laikrodis (pvz., sinchroninė atmintis).

Šiuo metu tankioje dvipusėje plokštėje nėra pakankamai bandymo taškų, o kiekvienas sudėtingas lustas turi turėti ribų nuskaitymo grandinę. Be

ribų nuskaitymas, plokštės lygio gamybos defektų paieška yra gana sudėtinga ir jų net negalima rasti. Naudojant ribų nuskaitymą, plokštės lygio testavimas yra labai paprastas

ir nepriklauso nuo lusto loginės grandinės. Ribų nuskaitymas taip pat gali sukonfigūruoti ATPG režimą lusto nuskaitymo grandinėje bet kuriame gamybos etape.